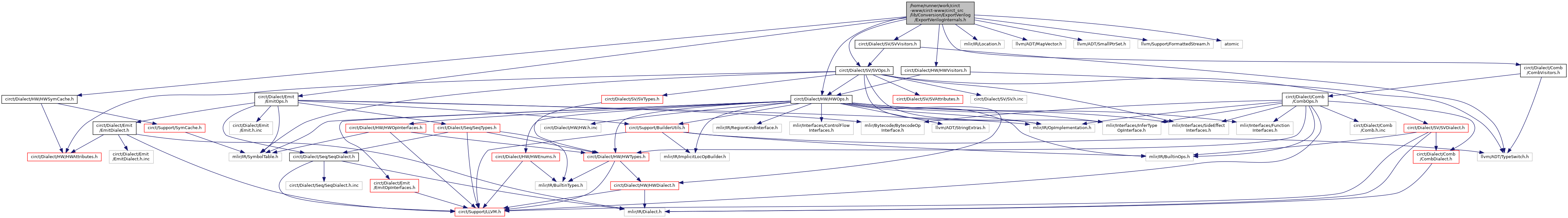

#include "circt/Dialect/Comb/CombVisitors.h"#include "circt/Dialect/Emit/EmitOps.h"#include "circt/Dialect/HW/HWOps.h"#include "circt/Dialect/HW/HWSymCache.h"#include "circt/Dialect/HW/HWVisitors.h"#include "circt/Dialect/SV/SVOps.h"#include "circt/Dialect/SV/SVVisitors.h"#include "mlir/IR/Location.h"#include "llvm/ADT/MapVector.h"#include "llvm/ADT/SmallPtrSet.h"#include "llvm/Support/FormattedStream.h"#include <atomic>

Include dependency graph for ExportVerilogInternals.h:

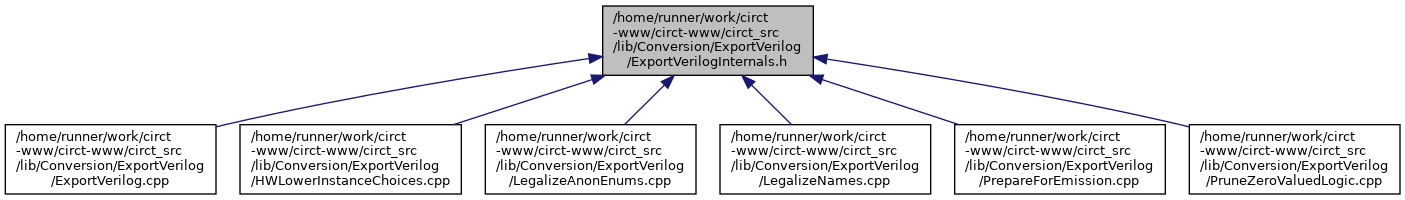

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | circt::ExportVerilog::GlobalNameTable |

| This class keeps track of global names at the module/interface level. More... | |

| struct | circt::ExportVerilog::NameCollisionResolver |

| struct | circt::ExportVerilog::FieldNameResolver |

| struct | circt::ExportVerilog::OpFileInfo |

| Information to control the emission of a single operation into a file. More... | |

| struct | circt::ExportVerilog::FileInfo |

| Information to control the emission of a list of operations into a file. More... | |

| class | circt::ExportVerilog::OpLocMap |

| Track the output verilog line,column number information for every op. More... | |

| struct | circt::ExportVerilog::OpLocMap::LineColPair |

| struct | circt::ExportVerilog::OpLocMap::LocationRange |

| class | circt::ExportVerilog::StringOrOpToEmit |

| This class wraps an operation or a fixed string that should be emitted. More... | |

| struct | circt::ExportVerilog::SharedEmitterState |

| This class tracks the top-level state for the emitters, which is built and then shared across all per-file emissions that happen in parallel. More... | |

Namespaces | |

| namespace | circt |

| The InstanceGraph op interface, see InstanceGraphInterface.td for more details. | |

| namespace | circt::ExportVerilog |

Typedefs | |

| using | circt::ExportVerilog::FileMapping = DenseMap< StringAttr, Operation * > |

| Mapping from symbols to file operations. | |

| using | circt::ExportVerilog::FragmentMapping = DenseMap< StringAttr, emit::FragmentOp > |

| Mapping from symbols to file operations. | |

Functions | |

| bool | circt::ExportVerilog::isSimpleReadOrPort (Value v) |

| Check if the value is from read of a wire or reg or is a port. | |

| StringAttr | circt::ExportVerilog::inferStructuralNameForTemporary (Value expr) |

| Given an expression that is spilled into a temporary wire, try to synthesize a better name than "_T_42" based on the structure of the expression. | |

| static bool | circt::ExportVerilog::isExpressionAlwaysInline (Operation *op) |

| Return true for operations that must always be inlined into a containing expression for correctness. | |

| StringRef | circt::ExportVerilog::getSymOpName (Operation *symOp) |

| Return the verilog name of the operations that can define a symbol. | |

| static bool | circt::ExportVerilog::isConstantExpression (Operation *op) |

| Return whether an operation is a constant. | |

| bool | circt::ExportVerilog::isVerilogExpression (Operation *op) |

| This predicate returns true if the specified operation is considered a potentially inlinable Verilog expression. | |

| bool | circt::ExportVerilog::isZeroBitType (Type type) |

| Return true if this is a zero bit type, e.g. | |

| bool | circt::ExportVerilog::isExpressionEmittedInline (Operation *op, const LoweringOptions &options) |

| Return true if this expression should be emitted inline into any statement that uses it. | |

| LogicalResult | circt::ExportVerilog::lowerHWInstanceChoices (mlir::ModuleOp module) |

| Generates the macros used by instance choices. | |

| LogicalResult | circt::ExportVerilog::prepareHWModule (Block &block, const LoweringOptions &options) |

| For each module we emit, do a prepass over the structure, pre-lowering and otherwise rewriting operations we don't want to emit. | |

| LogicalResult | circt::ExportVerilog::prepareHWModule (hw::HWEmittableModuleLike module, const LoweringOptions &options) |

| void | circt::ExportVerilog::pruneZeroValuedLogic (hw::HWEmittableModuleLike module) |

| GlobalNameTable | circt::ExportVerilog::legalizeGlobalNames (ModuleOp topLevel, const LoweringOptions &options) |

| Rewrite module names and interfaces to not conflict with each other or with Verilog keywords. | |