Creates a new Calyx component for each FuncOp in the program. More...

Public Member Functions | |

| LogicalResult | partiallyLowerFuncToComp (FuncOp funcOp, PatternRewriter &rewriter) const override |

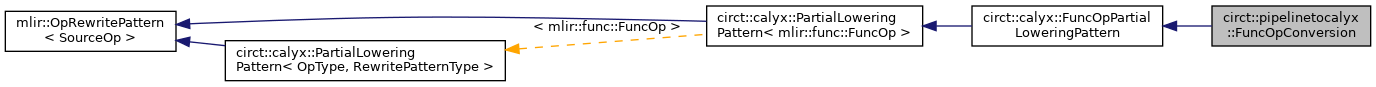

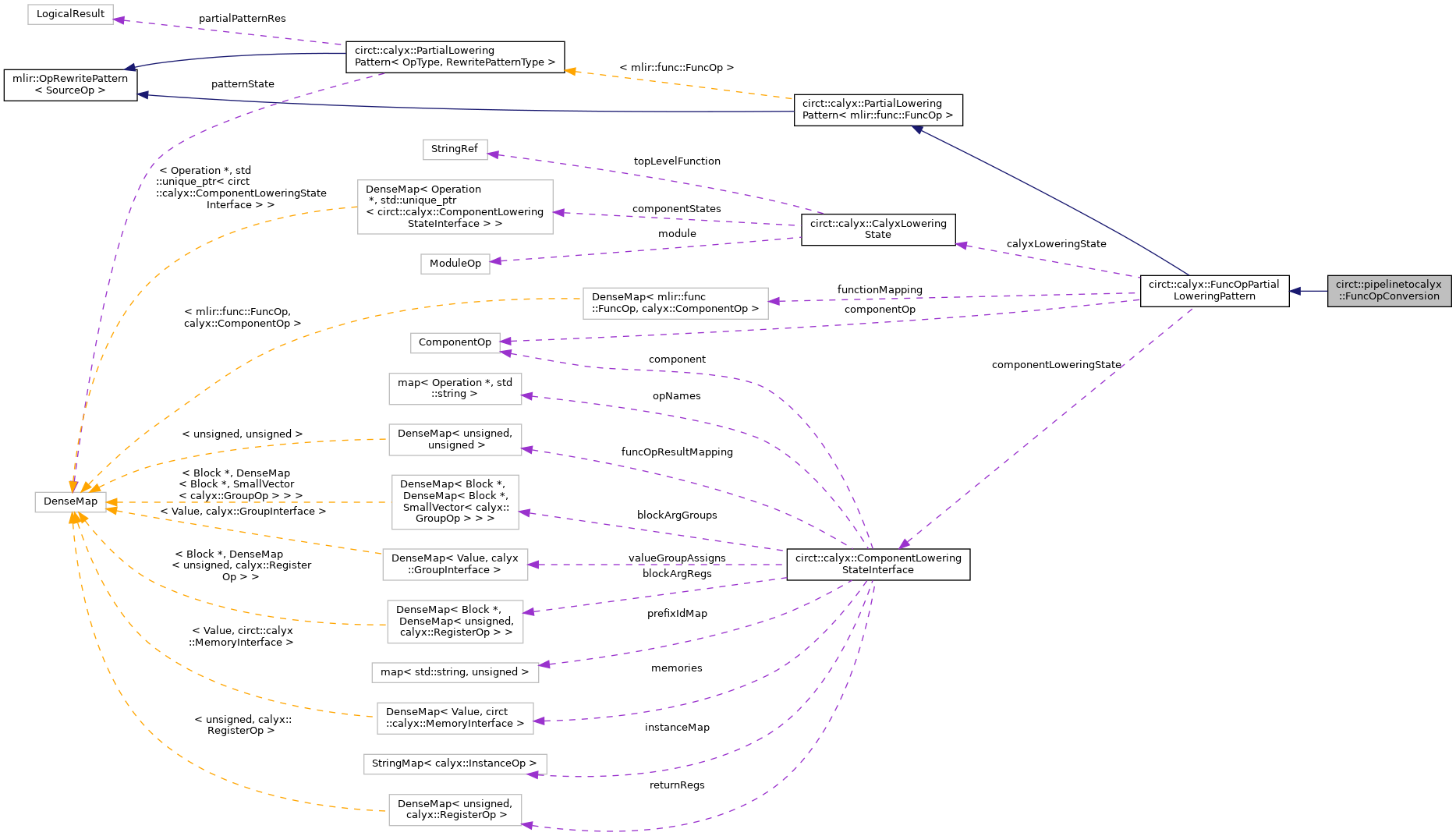

Public Member Functions inherited from circt::calyx::FuncOpPartialLoweringPattern Public Member Functions inherited from circt::calyx::FuncOpPartialLoweringPattern | |

| FuncOpPartialLoweringPattern (MLIRContext *context, LogicalResult &resRef, PatternApplicationState &patternState, DenseMap< mlir::func::FuncOp, calyx::ComponentOp > &map, calyx::CalyxLoweringState &state) | |

| LogicalResult | partiallyLower (mlir::func::FuncOp funcOp, PatternRewriter &rewriter) const override final |

| Entry point to initialize the state of this class and conduct the partial lowering. | |

| calyx::ComponentOp | getComponent () const |

| Returns the component operation associated with the currently executing partial lowering. | |

| template<typename T = ComponentLoweringStateInterface> | |

| T & | getState () const |

| CalyxLoweringState & | loweringState () const |

| Return the calyx lowering state for this pattern. | |

| virtual LogicalResult | partiallyLowerFuncToComp (mlir::func::FuncOp funcOp, PatternRewriter &rewriter) const =0 |

Public Member Functions inherited from circt::calyx::PartialLoweringPattern< mlir::func::FuncOp > Public Member Functions inherited from circt::calyx::PartialLoweringPattern< mlir::func::FuncOp > | |

| PartialLoweringPattern (MLIRContext *ctx, LogicalResult &resRef, PatternApplicationState &patternState) | |

| LogicalResult | matchAndRewrite (mlir::func::FuncOp op, PatternRewriter &rewriter) const override |

Additional Inherited Members | |

Protected Attributes inherited from circt::calyx::FuncOpPartialLoweringPattern Protected Attributes inherited from circt::calyx::FuncOpPartialLoweringPattern | |

| DenseMap< mlir::func::FuncOp, calyx::ComponentOp > & | functionMapping |

Detailed Description

Creates a new Calyx component for each FuncOp in the program.

Definition at line 775 of file LoopScheduleToCalyx.cpp.

Member Function Documentation

◆ partiallyLowerFuncToComp()

|

inlineoverride |

Maintain a mapping between funcOp input arguments and the port index which the argument will eventually map to.

Maintain a mapping between funcOp output indexes and the component output port index which the return value will eventually map to.

Maintain a mapping between an external memory argument (identified by a memref) and eventual component input- and output port indices that will map to the memory ports. The pair denotes the start index of the memory ports in the in- and output ports of the component. Ports are expected to be ordered in the same manner as they are added by calyx::appendPortsForExternalMemref.

Create I/O ports. Maintain separate in/out port vectors to determine which port index each function argument will eventually map to.

External memories

Single-port arguments

We've now recorded all necessary indices. Merge in- and output ports and add the required mandatory component ports.

Create a calyx::ComponentOp corresponding to the to-be-lowered function.

Mark this component as the toplevel.

Store the function-to-component mapping.

Rewrite funcOp SSA argument values to the CompOp arguments.

Register external memories

Create a mapping for the in- and output ports using the Calyx memory port structure.

Register the external memory ports as a memory interface within the component.

Definition at line 779 of file LoopScheduleToCalyx.cpp.

References circt::calyx::addMandatoryComponentPorts(), circt::calyx::MemoryPortsImpl::addrPorts, circt::calyx::appendPortsForExternalMemref(), circt::calyx::MemoryPortsImpl::done, circt::calyx::FuncOpPartialLoweringPattern::functionMapping, circt::calyx::CalyxLoweringState::getState(), circt::calyx::Input, circt::calyx::FuncOpPartialLoweringPattern::loweringState(), circt::calyx::normalizeType(), circt::calyx::Output, circt::calyx::MemoryPortsImpl::readData, circt::calyx::ComponentLoweringStateInterface::setFuncOpResultMapping(), circt::calyx::MemoryPortsImpl::writeData, and circt::calyx::MemoryPortsImpl::writeEn.

The documentation for this struct was generated from the following file:

- /home/runner/work/circt-www/circt-www/circt_src/lib/Conversion/LoopScheduleToCalyx/LoopScheduleToCalyx.cpp