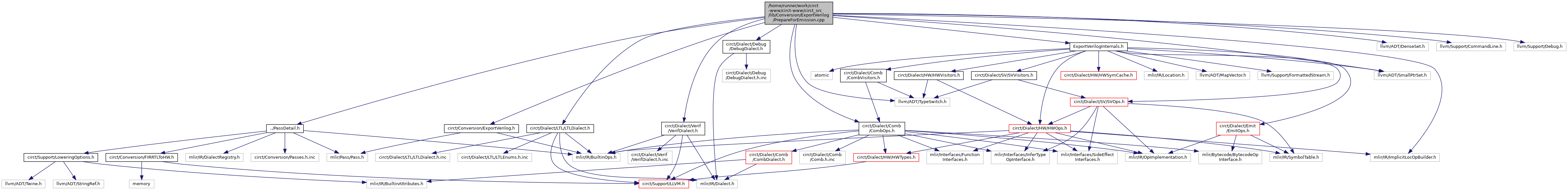

#include "ExportVerilogInternals.h"#include "circt/Conversion/ExportVerilog.h"#include "circt/Dialect/Comb/CombOps.h"#include "circt/Dialect/Debug/DebugDialect.h"#include "circt/Dialect/LTL/LTLDialect.h"#include "circt/Dialect/Verif/VerifDialect.h"#include "circt/Support/LoweringOptions.h"#include "circt/Support/ProceduralRegionTrait.h"#include "mlir/IR/ImplicitLocOpBuilder.h"#include "mlir/Interfaces/CallInterfaces.h"#include "mlir/Pass/Pass.h"#include "llvm/ADT/DenseSet.h"#include "llvm/ADT/SmallPtrSet.h"#include "llvm/ADT/TypeSwitch.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Debug.h"#include "circt/Conversion/Passes.h.inc"

Go to the source code of this file.

Classes | |

| struct | EmittedExpressionState |

| class | EmittedExpressionStateManager |

| This class handles information about AST structures of each expressions. More... | |

| struct | WireLowering |

Namespaces | |

| namespace | circt |

| The InstanceGraph op interface, see InstanceGraphInterface.td for more details. | |

Macros | |

| #define | DEBUG_TYPE "prepare-for-emission" |

| #define | GEN_PASS_DEF_PREPAREFOREMISSION |

Functions | |

| static bool | shouldSpillWire (Operation &op, const LoweringOptions &options) |

| static StringAttr | getArgName (Operation *op, size_t idx) |

| static void | spillWiresForInstanceInputs (HWInstanceLike op) |

| static void | replacePortWithWire (ImplicitLocOpBuilder &builder, Operation *op, Value result, StringRef name) |

| static StringAttr | getResName (Operation *op, size_t idx) |

| static void | lowerInstanceResults (HWInstanceLike op) |

| static void | lowerFunctionCallResults (Operation *op) |

| static void | lowerUsersToTemporaryWire (Operation &op, bool emitWireAtBlockBegin=false) |

| Emit an explicit wire or logic to assign operation's result. | |

| static void | lowerAlwaysInlineOperation (Operation *op, const LoweringOptions &options) |

| static std::pair< Block *, Block::iterator > | findLogicOpInsertionPoint (Operation *op) |

| static Value | lowerFullyAssociativeOp (Operation &op, OperandRange operands, SmallVector< Operation * > &newOps) |

| Lower a variadic fully-associative operation into an expression tree. | |

| static Operation * | rewriteAddWithNegativeConstant (comb::AddOp add, hw::ConstantOp rhsCst) |

| Transform "a + -cst" ==> "a - cst" for prettier output. | |

| static Operation * | lowerStructExplodeOp (hw::StructExplodeOp op) |

| static Operation * | findParentInNonProceduralRegion (Operation *op) |

| Given an operation in a procedural region, scan up the region tree to find the first operation in a graph region (typically an always or initial op). | |

| static bool | rewriteSideEffectingExpr (Operation *op) |

| This function is invoked on side effecting Verilog expressions when we're in 'disallowLocalVariables' mode for old Verilog clients. | |

| static bool | hoistNonSideEffectExpr (Operation *op) |

| This function is called for non-side-effecting Verilog expressions when we're in 'disallowLocalVariables' mode for old Verilog clients. | |

| static bool | isMovableDeclaration (Operation *op) |

| Check whether an op is a declaration that can be moved. | |

| static bool | reuseExistingInOut (Operation *op, const LoweringOptions &options) |

| If exactly one use of this op is an assign, replace the other uses with a read from the assigned wire or reg. | |

| static void | prettifyAfterLegalization (Block &block, const LoweringOptions &options, EmittedExpressionStateManager &expressionStateManager) |

| After the legalization, we are able to know accurate verilog AST structures. | |

| static void | buildWireLowerings (Block &block, SmallVectorImpl< WireLowering > &wireLowerings) |

Determine the insertion location of declaration and assignment ops for hw::WireOps in a block. | |

| static void | applyWireLowerings (Block &block, ArrayRef< WireLowering > wireLowerings) |

Materialize the SV wire declaration and assignment operations in the locations previously determined by a call to buildWireLowerings. | |

| static LogicalResult | legalizeHWModule (Block &block, const LoweringOptions &options) |

| For each module we emit, do a prepass over the structure, pre-lowering and otherwise rewriting operations we don't want to emit. | |

| static void | fixUpEmptyModules (hw::HWEmittableModuleLike module) |

Macro Definition Documentation

◆ DEBUG_TYPE

| #define DEBUG_TYPE "prepare-for-emission" |

Definition at line 37 of file PrepareForEmission.cpp.

◆ GEN_PASS_DEF_PREPAREFOREMISSION

| #define GEN_PASS_DEF_PREPAREFOREMISSION |

Definition at line 40 of file PrepareForEmission.cpp.

Function Documentation

◆ applyWireLowerings()

|

static |

Materialize the SV wire declaration and assignment operations in the locations previously determined by a call to buildWireLowerings.

This replaces all hw::WireOps with their appropriate SV counterpart.

Definition at line 859 of file PrepareForEmission.cpp.

References sv.WireOp::create(), sv.AssignOp::create(), and sv.ReadInOutOp::create().

Referenced by legalizeHWModule().

◆ buildWireLowerings()

|

static |

Determine the insertion location of declaration and assignment ops for hw::WireOps in a block.

This function tries to place the declaration point as late as possible, right before the very first use of the wire. It also tries to place the assign point as early as possible, right after the assigned value becomes available.

Definition at line 830 of file PrepareForEmission.cpp.

Referenced by legalizeHWModule().

◆ findLogicOpInsertionPoint()

|

static |

Definition at line 377 of file PrepareForEmission.cpp.

References findLogicOpInsertionPoint().

Referenced by findLogicOpInsertionPoint(), and legalizeHWModule().

◆ findParentInNonProceduralRegion()

|

static |

Given an operation in a procedural region, scan up the region tree to find the first operation in a graph region (typically an always or initial op).

By looking for a graph region, we will stop at graph-region #ifdef's that may enclose this operation.

Definition at line 464 of file PrepareForEmission.cpp.

References assert().

Referenced by hoistNonSideEffectExpr(), legalizeHWModule(), and rewriteSideEffectingExpr().

◆ fixUpEmptyModules()

|

static |

Definition at line 1362 of file PrepareForEmission.cpp.

References sv.WireOp::create(), hw.ConstantOp::create(), and sv.AssignOp::create().

Referenced by circt::ExportVerilog::prepareHWModule().

◆ getArgName()

|

static |

Definition at line 77 of file PrepareForEmission.cpp.

Referenced by spillWiresForInstanceInputs().

◆ getResName()

|

static |

Definition at line 144 of file PrepareForEmission.cpp.

Referenced by lowerInstanceResults().

◆ hoistNonSideEffectExpr()

|

static |

This function is called for non-side-effecting Verilog expressions when we're in 'disallowLocalVariables' mode for old Verilog clients.

It hoists non-constant expressions out to the top level so they don't turn into local variable declarations.

Definition at line 514 of file PrepareForEmission.cpp.

References findParentInNonProceduralRegion(), and circt::ExportVerilog::isExpressionAlwaysInline().

Referenced by legalizeHWModule().

◆ isMovableDeclaration()

|

static |

Check whether an op is a declaration that can be moved.

Definition at line 567 of file PrepareForEmission.cpp.

Referenced by legalizeHWModule(), and prettifyAfterLegalization().

◆ legalizeHWModule()

|

static |

For each module we emit, do a prepass over the structure, pre-lowering and otherwise rewriting operations we don't want to emit.

Definition at line 912 of file PrepareForEmission.cpp.

References applyWireLowerings(), assert(), buildWireLowerings(), sv.WireOp::create(), hw.ConstantOp::create(), sv.AssignOp::create(), hw.StructCreateOp::create(), sv.ReadInOutOp::create(), circt::LoweringOptions::disallowExpressionInliningInPorts, circt::LoweringOptions::disallowLocalVariables, circt::LoweringOptions::disallowPackedStructAssignments, findLogicOpInsertionPoint(), findParentInNonProceduralRegion(), hoistNonSideEffectExpr(), circt::ExportVerilog::isConstantExpression(), circt::ExportVerilog::isExpressionAlwaysInline(), isMovableDeclaration(), circt::ExportVerilog::isVerilogExpression(), legalizeHWModule(), lowerAlwaysInlineOperation(), lowerFullyAssociativeOp(), lowerFunctionCallResults(), lowerInstanceResults(), lowerStructExplodeOp(), lowerUsersToTemporaryWire(), circt::LoweringOptions::mitigateVivadoArrayIndexConstPropBug, reuseExistingInOut(), rewriteAddWithNegativeConstant(), rewriteSideEffectingExpr(), shouldSpillWire(), and spillWiresForInstanceInputs().

Referenced by legalizeHWModule(), and circt::ExportVerilog::prepareHWModule().

◆ lowerAlwaysInlineOperation()

|

static |

Definition at line 311 of file PrepareForEmission.cpp.

References assert(), circt::ExportVerilog::isExpressionAlwaysInline(), lowerAlwaysInlineOperation(), lowerUsersToTemporaryWire(), and shouldSpillWire().

Referenced by legalizeHWModule(), lowerAlwaysInlineOperation(), and reuseExistingInOut().

◆ lowerFullyAssociativeOp()

|

static |

Lower a variadic fully-associative operation into an expression tree.

This enables long-line splitting to work with them. NOLINTNEXTLINE(misc-no-recursion)

Definition at line 387 of file PrepareForEmission.cpp.

References assert(), and lowerFullyAssociativeOp().

Referenced by legalizeHWModule(), and lowerFullyAssociativeOp().

◆ lowerFunctionCallResults()

|

static |

Definition at line 199 of file PrepareForEmission.cpp.

References assert(), getBodyBlock(), and replacePortWithWire().

Referenced by legalizeHWModule().

◆ lowerInstanceResults()

|

static |

Definition at line 151 of file PrepareForEmission.cpp.

References sv.WireOp::create(), sv.AssignOp::create(), sv.ReadInOutOp::create(), getBodyBlock(), getResName(), and circt::ExportVerilog::isZeroBitType().

Referenced by legalizeHWModule().

◆ lowerStructExplodeOp()

|

static |

Definition at line 443 of file PrepareForEmission.cpp.

References hw.StructExtractOp::create().

Referenced by legalizeHWModule().

◆ lowerUsersToTemporaryWire()

|

static |

Emit an explicit wire or logic to assign operation's result.

This function is used to create a temporary to legalize a verilog expression or to resolve use-before-def in a graph region. If emitWireAtBlockBegin is true, a temporary wire will be created at the beginning of the block. Otherwise, a wire is created just after op's position so that we can inline the assignment into its wire declaration.

Definition at line 231 of file PrepareForEmission.cpp.

References sv.WireOp::create(), sv.AssignOp::create(), sv.ReadInOutOp::create(), and circt::ExportVerilog::inferStructuralNameForTemporary().

Referenced by legalizeHWModule(), lowerAlwaysInlineOperation(), and prettifyAfterLegalization().

◆ prettifyAfterLegalization()

|

static |

After the legalization, we are able to know accurate verilog AST structures.

So this function walks and prettifies verilog IR with a heuristic method specified by options.wireSpillingHeuristic based on the structures. Also move the declarations to the top of the block when disallowDeclAssignments is set.

Definition at line 785 of file PrepareForEmission.cpp.

References circt::LoweringOptions::disallowDeclAssignments, isMovableDeclaration(), circt::ExportVerilog::isVerilogExpression(), lowerUsersToTemporaryWire(), prettifyAfterLegalization(), and EmittedExpressionStateManager::shouldSpillWireBasedOnState().

Referenced by circt::ExportVerilog::prepareHWModule(), and prettifyAfterLegalization().

◆ replacePortWithWire()

|

static |

Definition at line 115 of file PrepareForEmission.cpp.

References sv.WireOp::create(), sv.AssignOp::create(), and sv.ReadInOutOp::create().

Referenced by lowerFunctionCallResults().

◆ reuseExistingInOut()

|

static |

If exactly one use of this op is an assign, replace the other uses with a read from the assigned wire or reg.

This assumes the preconditions for doing so are met: op must be an expression in a non-procedural region.

Definition at line 680 of file PrepareForEmission.cpp.

References sv.ReadInOutOp::create(), circt::ExportVerilog::isExpressionAlwaysInline(), and lowerAlwaysInlineOperation().

Referenced by legalizeHWModule().

◆ rewriteAddWithNegativeConstant()

|

static |

Transform "a + -cst" ==> "a - cst" for prettier output.

This returns the first operation emitted.

Definition at line 426 of file PrepareForEmission.cpp.

References hw.ConstantOp::create().

Referenced by legalizeHWModule().

◆ rewriteSideEffectingExpr()

|

static |

This function is invoked on side effecting Verilog expressions when we're in 'disallowLocalVariables' mode for old Verilog clients.

This ensures that any side effecting expressions are only used by a single BPAssign to a sv.reg or sv.logic operation. This ensures that the verilog emitter doesn't have to worry about spilling them.

This returns true if the op was rewritten, false otherwise.

Definition at line 480 of file PrepareForEmission.cpp.

References assert(), sv.ReadInOutOp::create(), and findParentInNonProceduralRegion().

Referenced by legalizeHWModule().

◆ shouldSpillWire()

|

static |

Definition at line 69 of file PrepareForEmission.cpp.

References circt::ExportVerilog::isExpressionEmittedInline(), and circt::ExportVerilog::isVerilogExpression().

Referenced by legalizeHWModule(), and lowerAlwaysInlineOperation().

◆ spillWiresForInstanceInputs()

|

static |

Definition at line 84 of file PrepareForEmission.cpp.

References sv.WireOp::create(), sv.AssignOp::create(), sv.ReadInOutOp::create(), getArgName(), getBodyBlock(), and circt::ExportVerilog::isSimpleReadOrPort().

Referenced by legalizeHWModule().